实验目的

理解主存地址基本概念,理解存储位扩展基本思想,并能利用相关原理构建能同时支持字节、半字、字访问的存储子系统。

主要任务

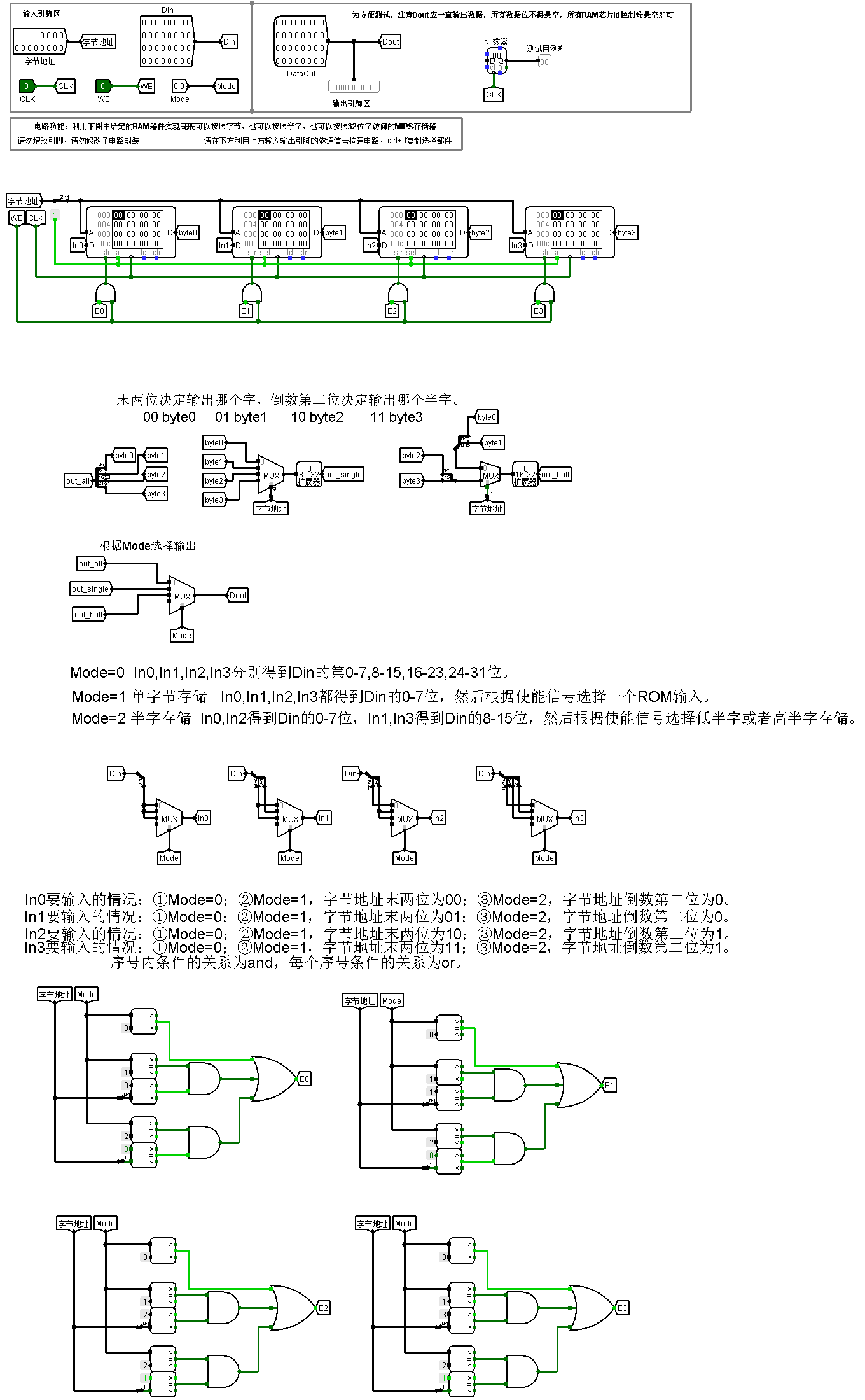

Logisim 中 RAM 组件只能提供固定的地址位宽,数据输出也只能提供固定的数据位宽,访问时无法同时支持字节/半字/字三种访问模式,实验要求利用 4 个 8 位的 RAM 组件进行扩展,设计完成既能按照 8 位、也能按 16 位、也能按照 32 位进行读写访问的 32 位存储器。

Addr 为 12 字节地址输入(字访问时忽略最低两位,半字访问时忽略最低位,倒数第二位片选,字节访问时,低两位进行片选)。Din 为 32 位写入数据 (不同访问模式有效数据均存放在最低位,高位忽略)。Mode 为访问模式控制位(00 表示字访问,01 表示 1 字节访问,10 表示 2 字节访问)。WE 是写使能,1 表示写入,0 表示读出。Dout 是读出数据 (不同访问模式有效数据均存放在最低位,高位补零)。

实验原理

Addr 为 12 字节地址,低两位为片选地址,高 10 位为 RAM 的块内地址,每一个 RAM 可输出一个字节。

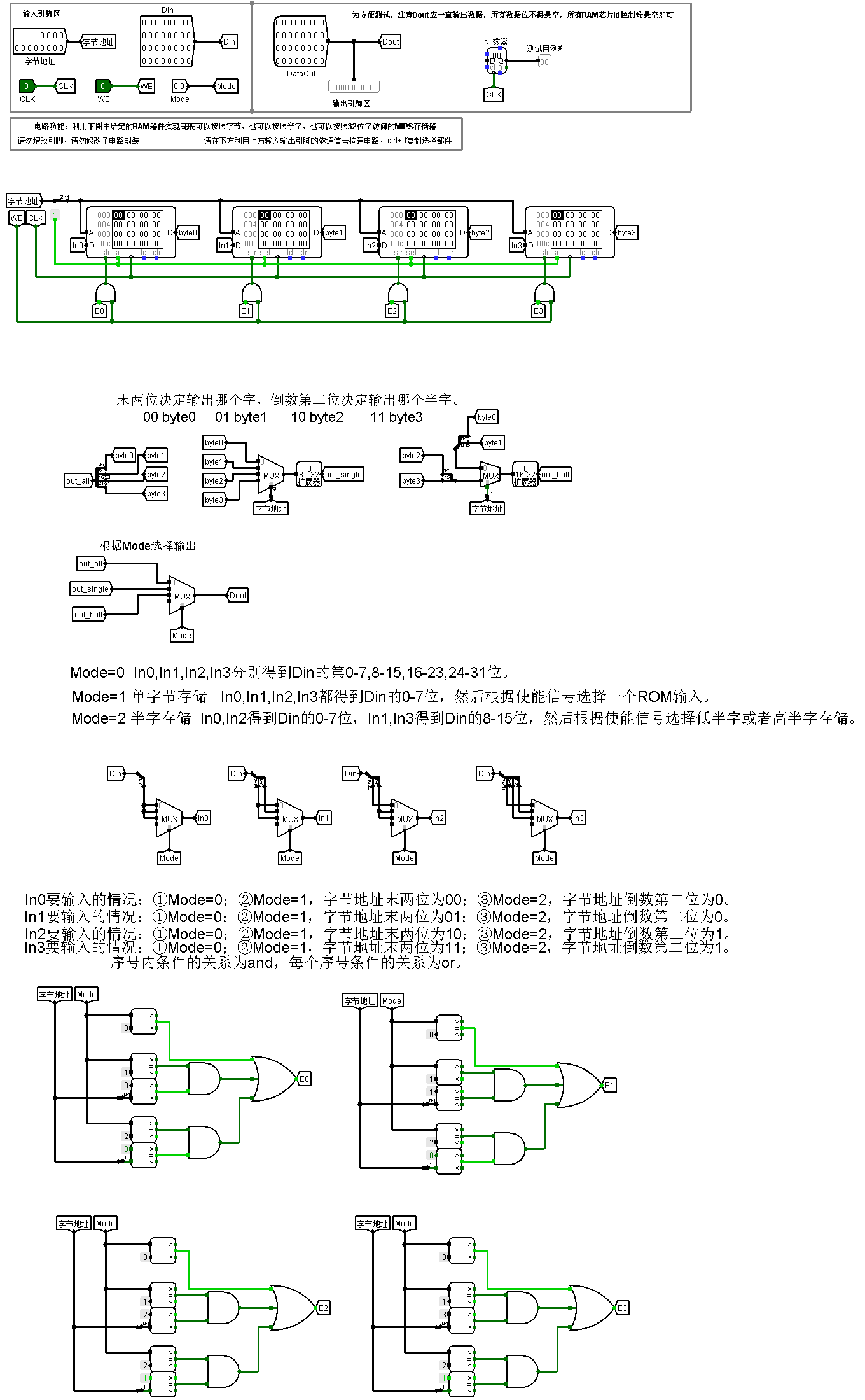

先考虑输出。整个字输出时,将四个 RAM 的数据全部输出。单字输出时根据字节地址末两位,选择一个 RAM 输出。半字输出时,若地址末两位为 00 或01,输出的是 0 号和 1 号 RAM 组成的半字;否则,输出 2 号和 3 号 RAM 组成的半字;因此片选为字节地址的倒数第二位。

再考虑输入,定义每一个 RAM 的输入为 In0,In1,In2,In3。整字输入时,In0,In1,In2,In3 分别得到 Din 的第 0∼7,8∼15,16∼23,24∼31 位。单字输入时,根据忽略高位的原则,In0,In1,In2,In3 都得到 Din 的第 0∼7 位,然后根据写入片选信号选择一个 RAM 输入。半字输入时,根据边界对齐和忽略高位的原则,In0,In2 得到 Din 的第 0∼7 位,In1,In3 得到 Din 的第 8∼15 位,然后根据写入的片选信号选择高半字或低半字存储。

接下来分析写入数据时的片选信号,我们可以考虑 In0,In1,In2,In3 的输入条件(根据 Mode 分类讨论)。若要输入 In0:① Mode=1;② Mode=2,字节地址末两位为 00;③ Mode=3,字节地址倒数第二位为 0。若要输入 In1:① Mode=1;② Mode=2,字节地址末两位为 01;③ Mode=3,字节地址倒数第二位为 0。若要输入 In2:① Mode=1;② Mode=2,字节地址末两位为 10;③ Mode=3,字节地址倒数第二位为 1。若要输入 In3:① Mode=1;② Mode=2,字节地址末两位为 11;③ Mode=3,字节地址倒数第二位为 1。

可构造数字逻辑电路得到输入的片选信号,与写使能信号通过或门,即可确定是否输入数据。

综上所述,设计完成了既能按照 8 位、也能按 16 位、也能按照 32 位进行读写访问的 32 位存储器。

电路图