MIPS运算器设计实验

实验目的

理解 的基本构成,掌握 中各种运算组件的使用方法,熟悉多路选择器的使用,能利用前述实验完成的 位加法器、 中的运算组件构造指定规格的 单元。

主要任务

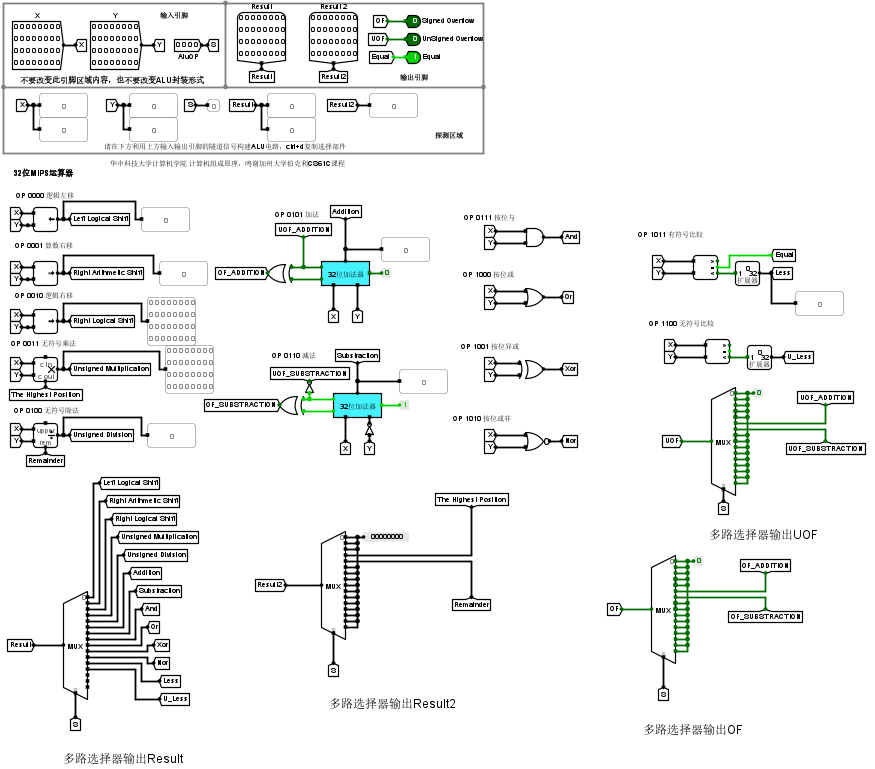

利用前面实验封装好 位加法器以及 平台中现有运算部件,构建一个 位算术逻辑运算单元(禁用 系统自带的加法器,减法器),可支持算术加、减、乘、除,逻辑与、或、非、异或运算、逻辑左移、逻辑右移、算术右移运算,支持常用程序状态标志(有符号溢出 、无符号溢出 ,结果相等),在主电路中详细测试自己封装的 ,并分析该运算器的优缺点。

实验原理

逻辑左移、逻辑右移、算数右移用移位器实现。

无符号乘法用乘法器实现, 的乘法器自带高比特位输出;无符号除法用除法器实现, 的除法器自带余数输出。

加法由之前做好的 位快速加法器实现,当最高位 位向 位有进位时,无符号加法产生溢出,即 ;当最高数据位和符号位进位不同步时,有符号加法产生溢出,即 。减法同样由 位快速加法器实现,求 时,输入 和 ,并令 ,实现求补操作;同加法类似,,。

逻辑运算与、或、非、异或、或非可由四种逻辑门实现。

有符号数比较和无符号数比较可由比较器实现。

设计好所有计算电路后,根据操作码,用多路选择器选择一个结果输出。

电路图

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 11D_Beyonder's Blog!