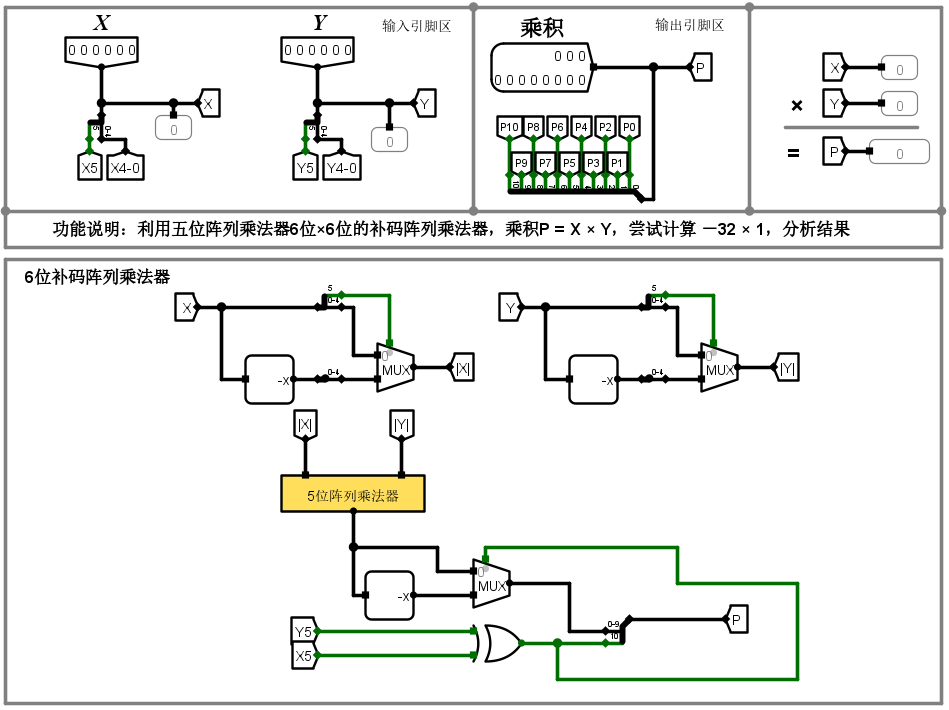

6位有符号补码阵列乘法器设计实验

实验目的

掌握补码阵列乘法器的实现原理。

主要任务

在 位补码阵列乘法器中利用 位阵列乘法器以及求补器等部件实现补码阵列乘法器。

实验原理

为符号位,其余为 位为数值位。

由于补码乘法中的乘数、被乘数和成绩的结果都以补码方式给出,为能利用无符号阵列乘法器,需要在运算前将以补码方式出现的被乘数和乘数先变成无符号数,因此需要设计求补电路。此外,无符号的阵列乘法器的输出结果是无符号数,为将结果变成补码,还需再最后增加一个求补电路。结果的符号位由异或门 产生,作为结果求补的控制信号。

接下来说明求补电路的设计,当输入数字 的符号位为 ,进行求补操作,否则不作任何改动;可利用分线器得到 和 , 作为多路选择器的选择信号, 送入求补器,输出补码。

若5位阵列乘法器结果的符号位为 ,则要对 位阵列乘法器输出结果求补,否则直接输出结果;此步骤仍然用多路选择器实现,选择信号为 。

电路图

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 11D_Beyonder's Blog!