5位无符号阵列乘法器设计实验

实验目的

掌握阵列乘法器的实现原理,能够分析阵列乘法器的性能,能在 中绘制阵列乘法器电路。

主要任务

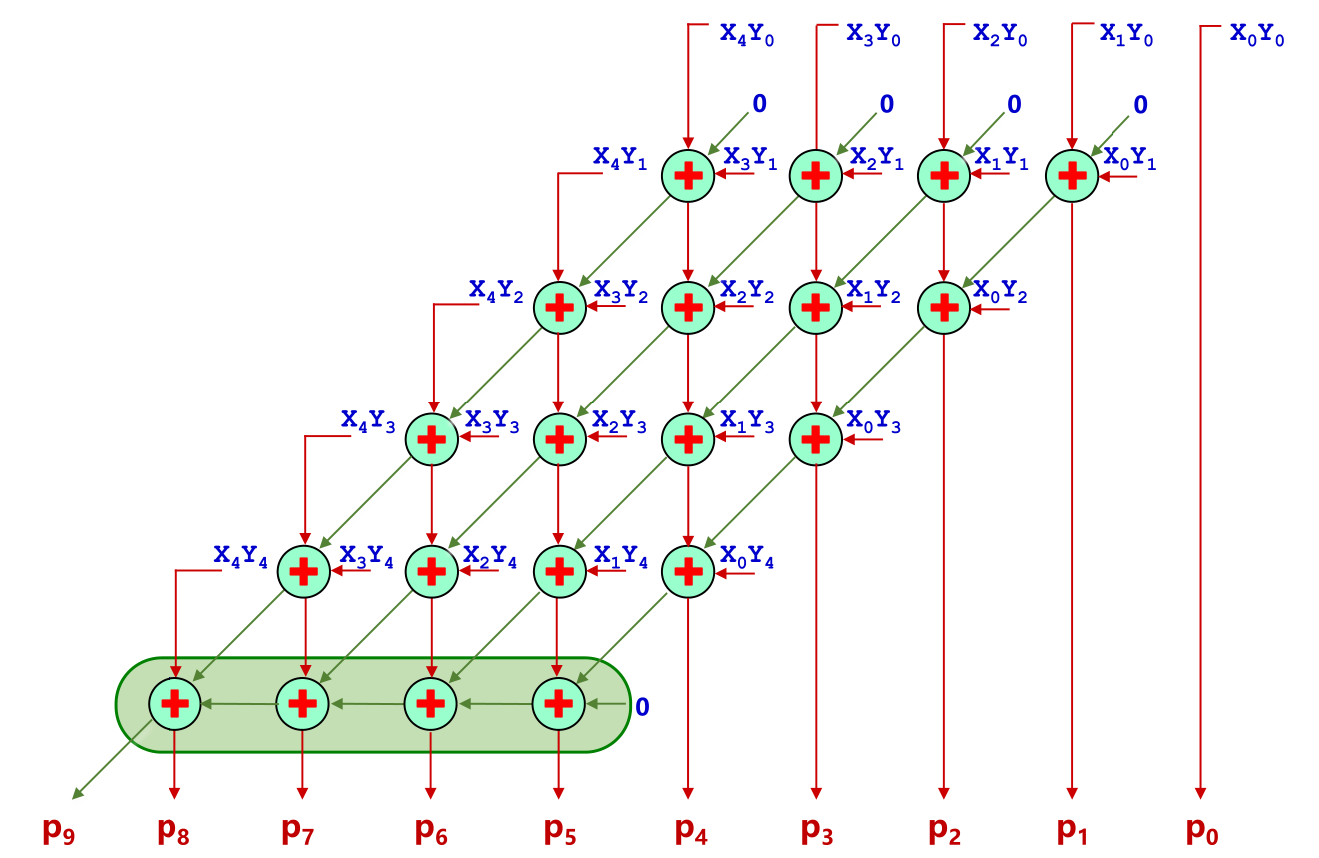

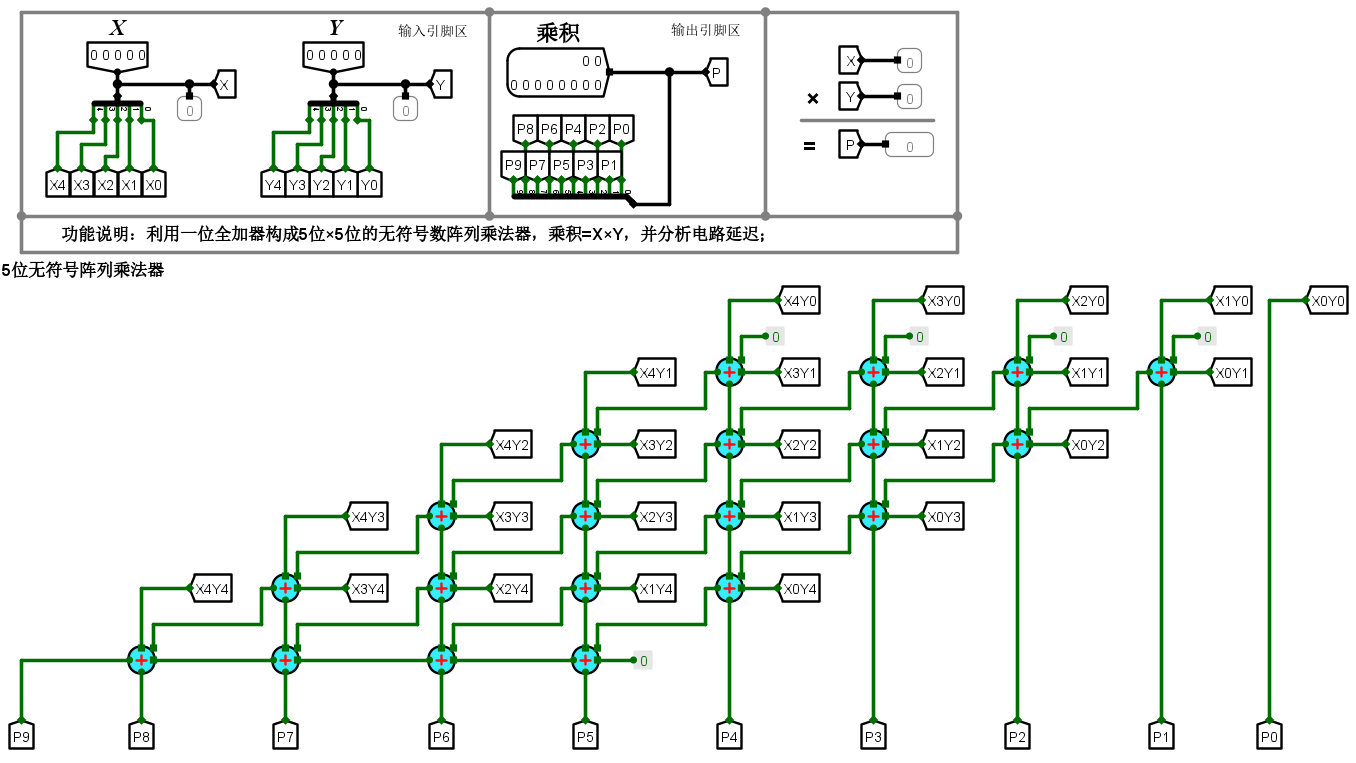

在 位阵列乘法器中实现斜向进位的阵列乘法器。其中 为5位被乘数和乘数, 为乘积输出,阵列乘法所需的 按位与的乘积项已经通过辅助电路生成,所有乘积项均通过隧道标签给出,用户只需要在已给出的电路框架中进行简单连线即可完成 位阵列乘法器。

实验原理

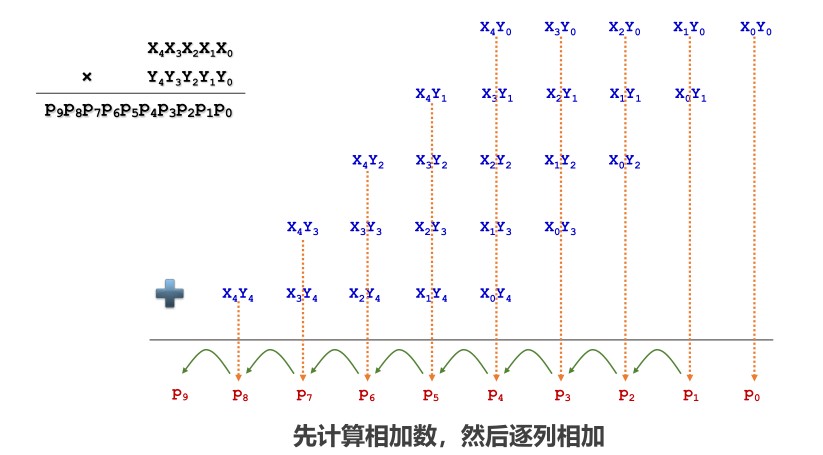

原理来自手工计算乘法。当且仅当 时相乘为 ,因此每一位的相乘通过一个与门实现。

每一列的累加用多个 实现,除最后一行的加法器外,每个 的进位输出到下一行相邻高位 的进位输入端。第 行阵列加法器进位为常量 ,第 行阵列加法器接收第 行加法器的进位……第 行加法器采用横向进位,接收第 行加法器的进位。

电路图

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 11D_Beyonder's Blog!