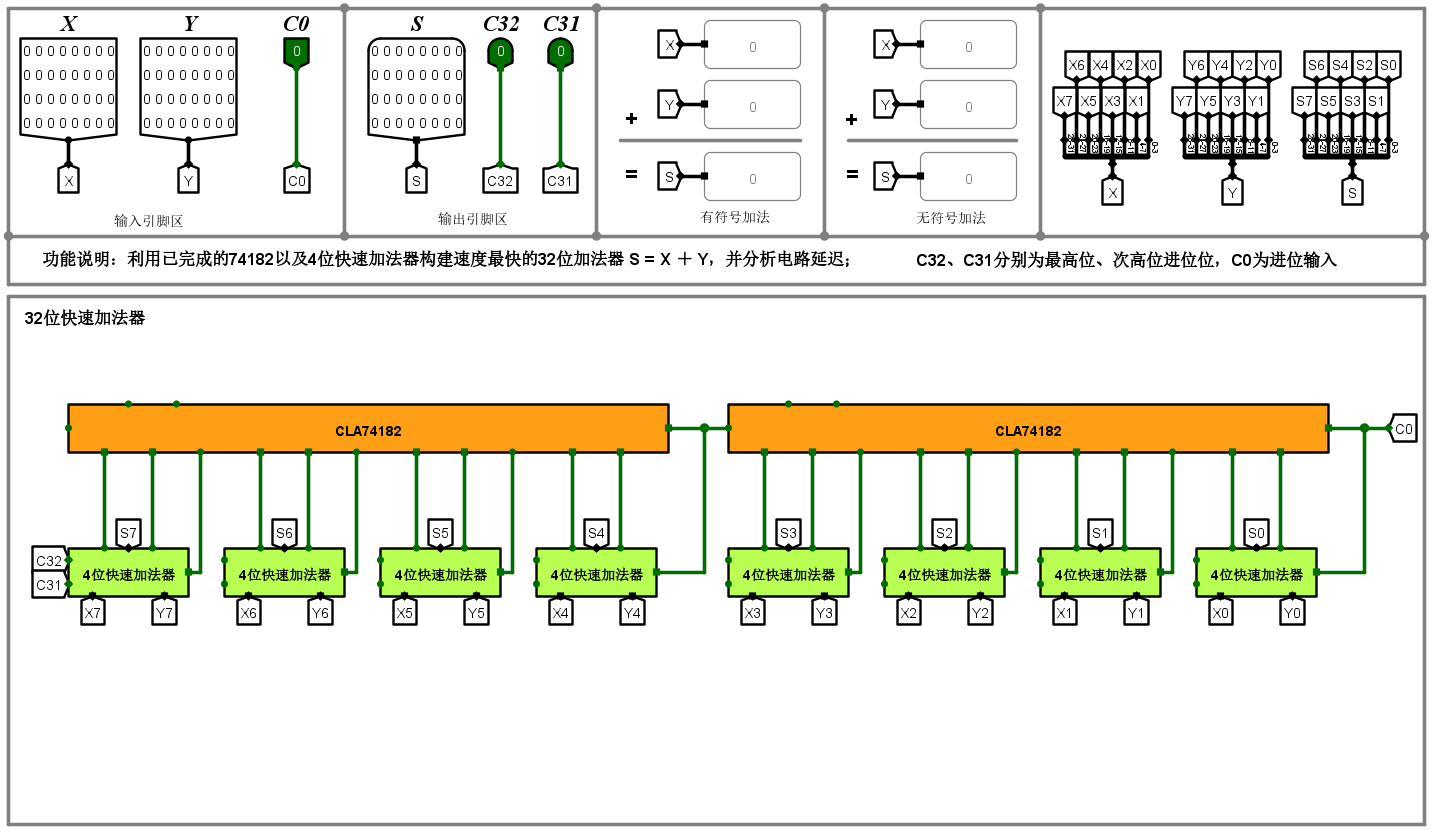

32位快速加法器设计实验

实验目的

帮助理解成组进位产生函数,成组进位传递函数的概念,熟悉 平台子电路的概念,能利用前述实验封装好的 位先行进位子电路以及 位快速加法器子电路构建 位快速加法器,并能利用相关知识分析对应电路的时间延迟,理解电路并行的概念。

主要任务

利用 位快速加法器以及先行进位电路构建 位快速加法器,并探讨其时间延迟。 为 位被相加数, 为进位输入, 为和数输出, 为进位输出, 为有符号加法运算溢出信号。

实验原理

个 位加法器直接串联, 进位输入采用上层的进位输出。

电路图

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 11D_Beyonder's Blog!