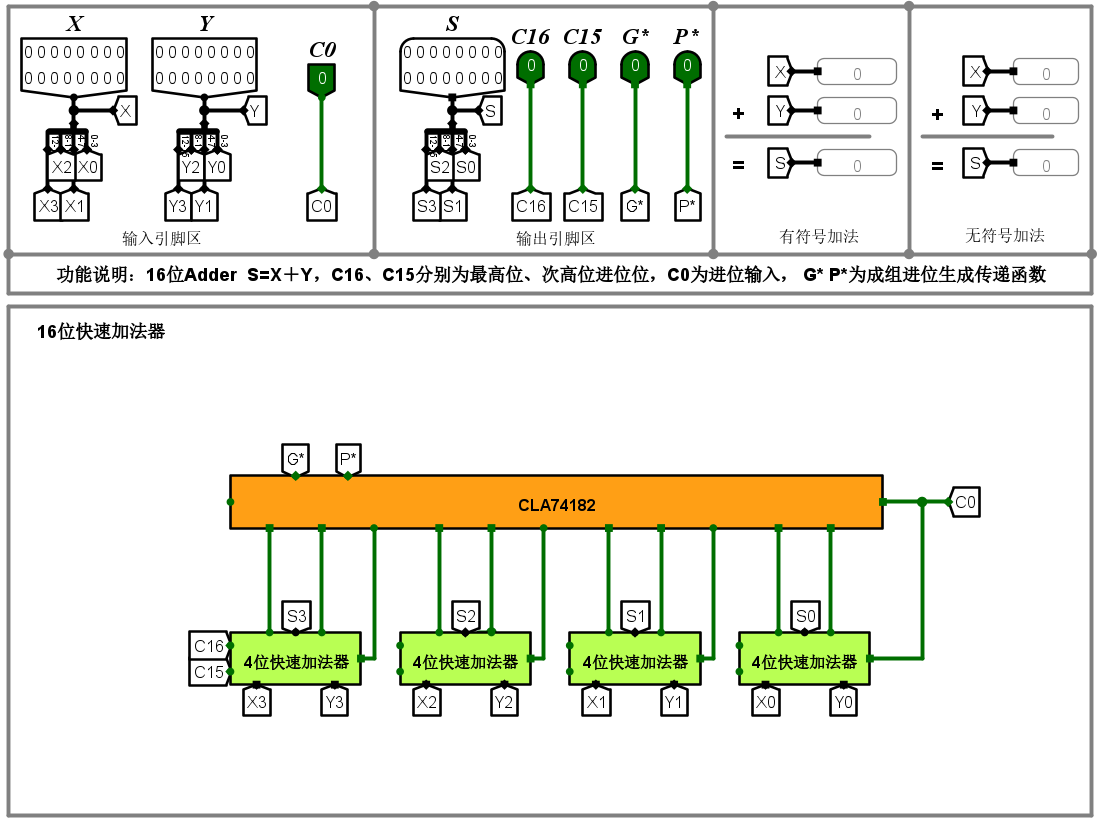

16位快速加法器设计实验

实验目的

帮助理解成组进位产生函数,成组进位传递函数的概念,熟悉 平台子电路的概念,能利用前述实验封装好的 位先行进位子电路以及 位快速加法器子电路构建 位,并能利用相关知识分析对应电路的时间延迟,理解电路并行的概念。

主要任务

利用四位先行进位电路和四位快速加法器构造十六位组间先行进位,组内先行进位快速加法器,并验证其功能是否正常。 为 位被相加数, 为进位输入, 为和数输出, 为进位输出, 为 位成组进位生成函数和成组进位传递函数。

实验原理

将 分成四部分 ,每部分占四位。用 位先行加法器得到 的结果 ,并输出 位成组进位;将 位成组进位信息输入到一个 模块中,得到 的进位输入。 模块 的输出引脚输出 位成组进位传递函数和成组进位生成函数。

例如, 的 位成组进位函数为 ,将 作为进位传递函数和进位生成函数传入 模块,得到 的进位为 。

电路图

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 11D_Beyonder's Blog!