实验目的

掌握快速加法器中先行进位的原理,能利用相关知识设计四位先行进位电路,并利用设计的四位先行进位电路构造四位快速加法器,能分析对应电路的时间延迟。

主要任务

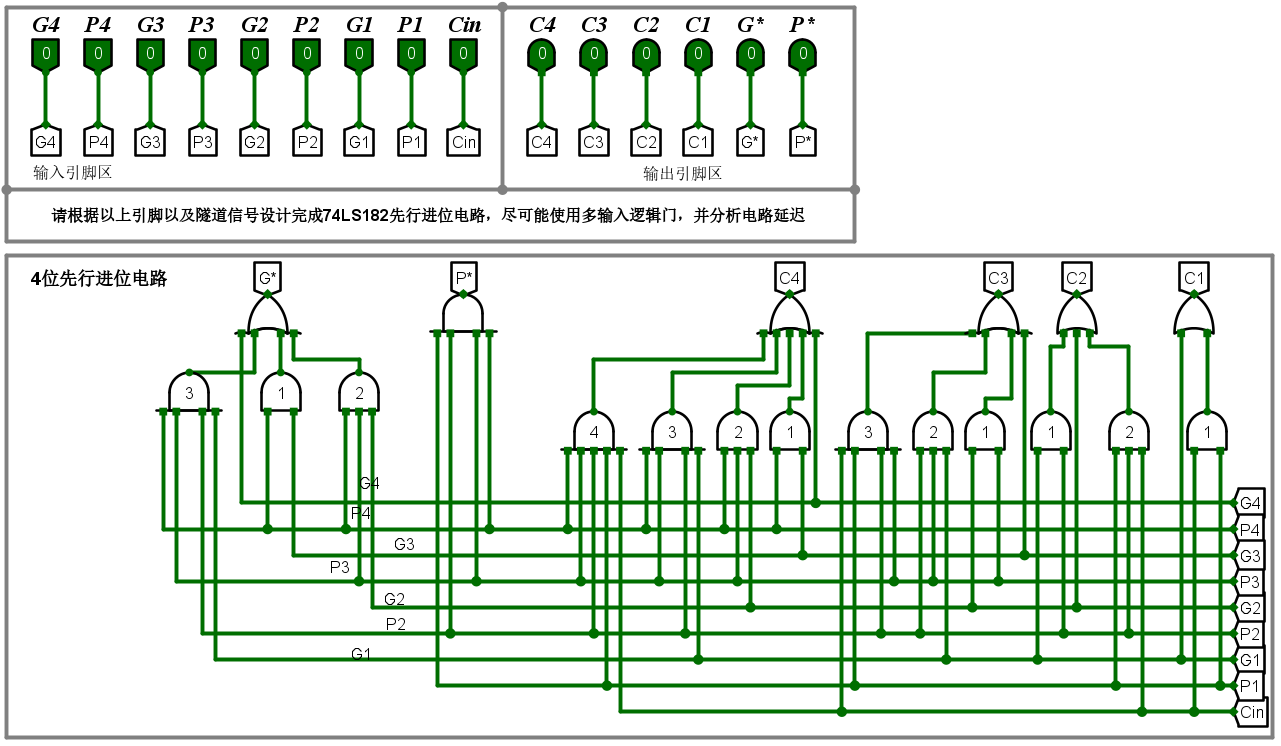

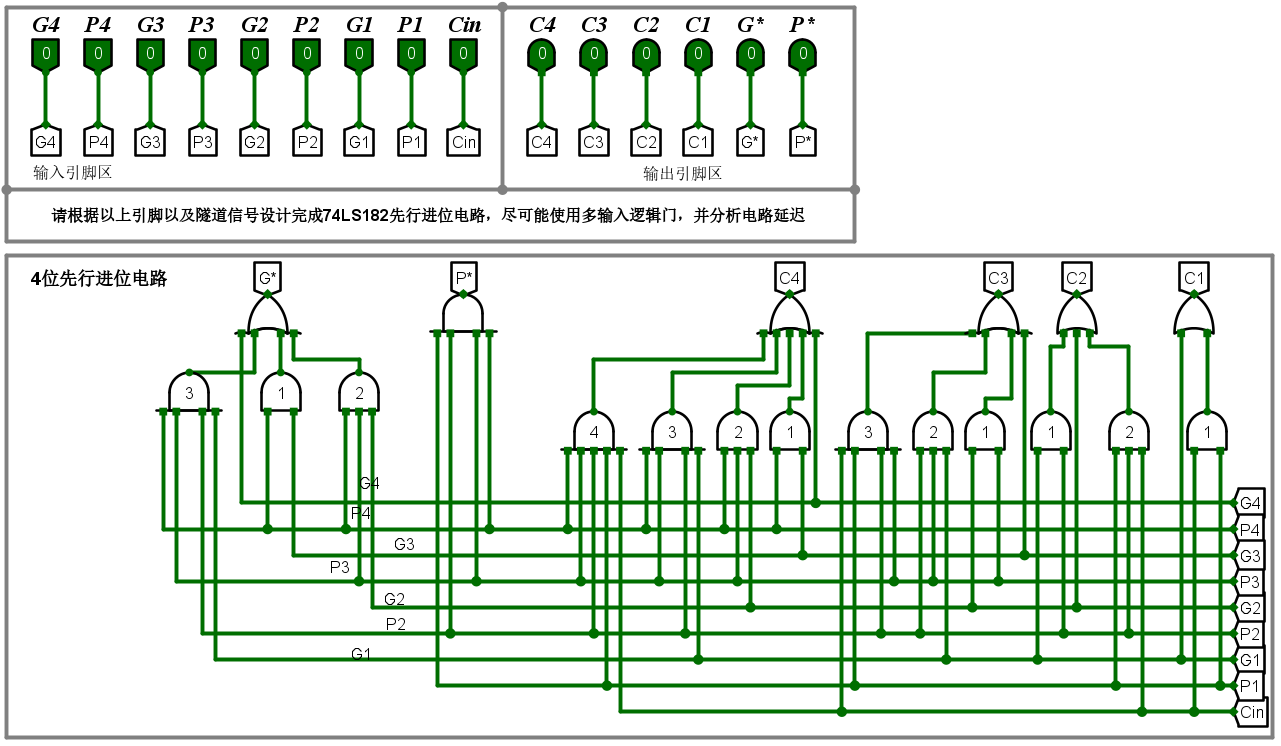

在 Logisim 中打开 alu.circ文件,按照定义的输入输出引脚,在对应子电路中实现可级联的四位先行进位电路。其中,Gi,Pi 是进位生成函数和传递函数,Cin 为进位输入,C1∼C4 为进位输出,G∗,P∗ 为成组进位生成函数和成组进位传递函数。

实验原理

对于 X+Y 的运算结果 S 的第 i 位 Si,有 Si=Xi⊕Yi⊕Ci−1(Ci−1 为前一位的进位输出)。对于 Ci,若 Xi=Yi=1,则产生进位;若 Xi⊕Yi=0,但是 Ci−1=1,仍然可以产生进位;因此,Ci=XiYi+(Xi⊕Yi)Ci−1。

定义 Gi=XiYi,Pi=Xi⊕Yi。则有 Ci=Gi+PiCi−1,按照此递推关系,得到

$$

\begin{cases}C_1=G_1+P_1C_0\\

C_2=G_2+P_2G_1+P_2P_1C_0\\

C_3=G_3+P_3G_2+P_3P_2G_1+P_3P_2P_1C_0\\

C_4=G_4+P_4G_3+P_4P_3G_2+P_4P_3P_2G_1+P_4P_3P_2P_1C_0\end{cases}

$$

四位为一组,有 G∗=G4+P4G3+P4P3G2+P4P3P2G1,P∗=P4P3P2P1。

电路图