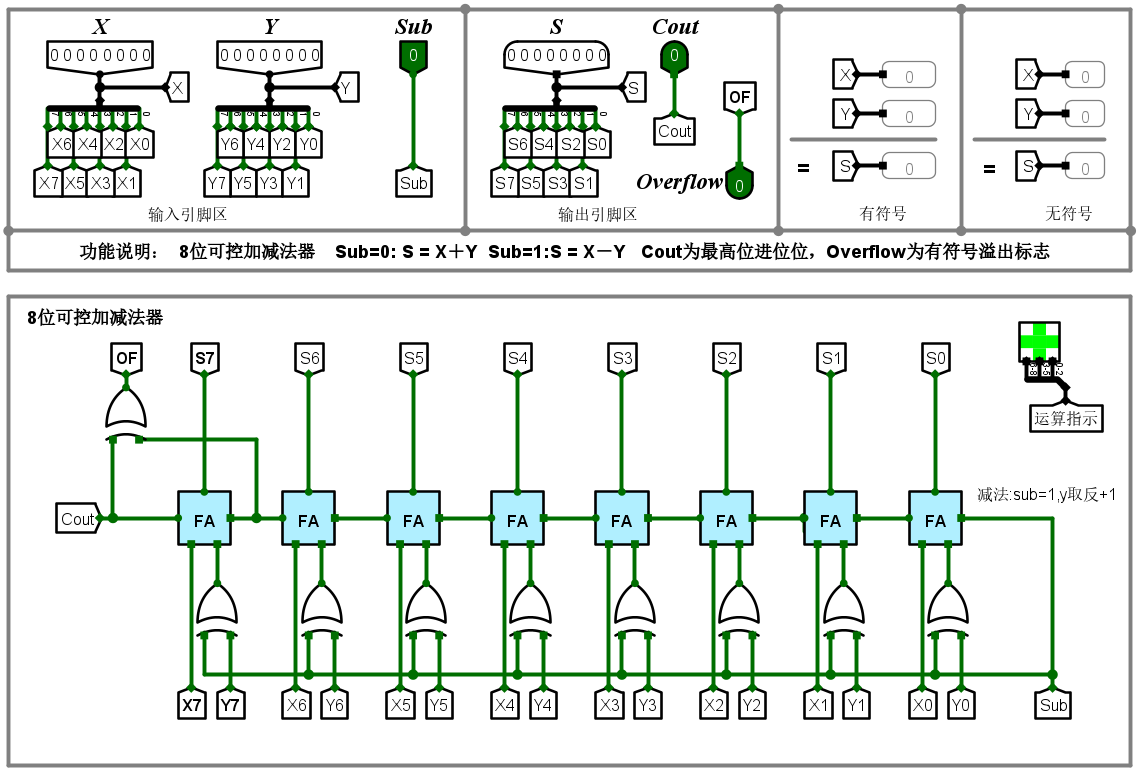

8位可控加减法电路设计实验

实验目的

帮助学生掌握一位全加器的实现逻辑,掌握多位可控加减法电路的实现逻辑,熟悉 平台基本功能,能在 中实现多位可控加减法电路。

主要任务

在 中打开 文件,在对应子电路中利用已经封装好的一位全加器设计 位串行可控加法电路。定义 为两输入数字, 为加减控制信号, 为运算结果输出, 为进位输出, 为有符号运算溢出位。

实验原理

利用一位全加器作为基本的加法单元,低位 的进位输出直接送入相邻的高位 的进位输入,构成一个串行进位链。

为 时,实现的是 位串行加法器。 为 时,要实现 。若实现的是减法, 需要转化成其补码形式(按位取反再加 ),实现方式是将 与 进行异或运算, 作为运算 的进位输入,如此就对送入加法器的 进行了一次求补操作。于是,当 ,即使经过为实现减法而设计的求补电路,对运算结果仍然不会产生影响,实现的仍旧是 ;而当 ,实现 。 经过求补电路后,同 一起输入 ,输出对应的 。

符号溢出根据运算过程中最高数据位的进位与符号位的进位位是否一致进行检测。设运算时最高有效数据位产生的进位信号为 ,符号位产生的进位信号为,令 。当且仅当 两者同步,即 时,才不会发生溢出。在本实验背景下, 即为 , 即为 。

电路图

本博客所有文章除特别声明外,均采用 CC BY-NC-SA 4.0 许可协议。转载请注明来自 11D_Beyonder's Blog!